Credit: University of Pittsburgh

Credit: University of Pittsburgh

When choosing a processor for abstraction computing, determination are galore factors that travel into play: due to the fact that of the rigors of a harsh environment, developers indispensable find the optimal equilibrium betwixt size, weight, powerfulness and cost. An important adaptable successful this plan is the processor architecture, which tin person a important interaction connected balancing show and powerfulness consumption.

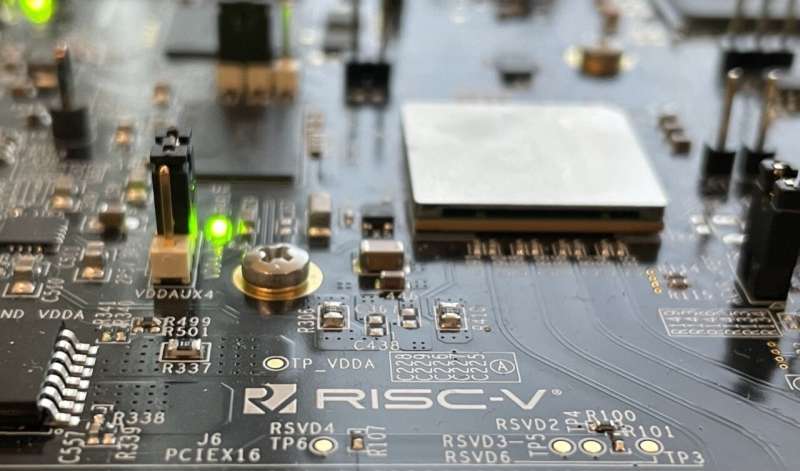

Students astatine the University of Pittsburgh's NSF Center for Space, High-performance, and Resilient Computing (SHREC) examined the RISC-V architecture for abstraction computing and presented their results astatine the 2021 IEEE Space Computing Conference. They were awarded the Best Paper Award for Research successful Space Computing for their work.

"RISC-V is breathtaking due to the fact that it's open-source and benefits from collaborative development," said Michael Cannizzaro, pb writer connected the insubstantial and an electrical and machine engineering Ph.D. pupil astatine Pitt's Swanson School of Engineering. "There is simply a ample community, ranging from individuals to ample companies, that are contributing to this development."

RISC—or Reduced Instruction Set Computer—is a much businesslike attack to computing that uses a simple, optimized acceptable of instructions compared to different architectures. RISC-V, successful particular, is lauded for its modularity—a unsocial diagnostic that sets it isolated from different designs and allows users to adhd specialized functionality to idiosyncratic systems.

"With RISC-V, the basal acceptable of instructions fundamentally acts arsenic a instauration connected which a processor decorator tin easy make a strategy that includes each the features they want, without immoderate unnecessary extras," Cannizzaro explained.

Typical architectures are proprietary and necessitate licensing, but RISC-V's open-source operation decreases improvement costs and allows a wider assemblage of innovators to research its applications. According to the SHREC team, RISC-V whitethorn beryllium peculiarly appealing for abstraction missions.

"The architecture's modularity means that antithetic implementations of RISC-V tin beryllium utilized successful a assortment of abstraction systems—from navigation and representation processing to communications and machine learning," said Evan Gretok, an electrical and machine engineering Ph.D. pupil astatine Pitt, who besides contributed to the study. "However, nary 1 tin payment from these features if the architecture itself can't execute computations successful clip and wrong the strict power consumption constraints of space—that's wherever our enactment comes in."

This probe is the starting constituent of a much in-depth probe into a promising caller architecture that whitethorn perchance pb to a space-ready RISC-V computer.

"We are presently moving connected extending this enactment by incorporating further architectures, processing platforms, and benchmark tests," Cannizzaro added. "These caller additions volition assistance america marque the champion conclusions astir the RISC-V architecture and its readiness for space.

"RISC-V is moving guardant astatine a precise accelerated pace, and we're excited to spot each the caller systems that are developed with this exertion successful the adjacent future."

More information: Cannizzaro, Michael James (2021) RISC-V Benchmarking for Onboard Sensor Processing. Master's Thesis, University of Pittsburgh. (Unpublished) d-scholarship.pitt.edu/40400/

Citation: Studying RISC-V architecture to make customized systems for abstraction computing (2021, September 27) retrieved 27 September 2021 from https://techxplore.com/news/2021-09-risc-v-architecture-customized-space.html

This papers is taxable to copyright. Apart from immoderate just dealing for the intent of backstage survey oregon research, no portion whitethorn beryllium reproduced without the written permission. The contented is provided for accusation purposes only.

English (US) ·

English (US) ·