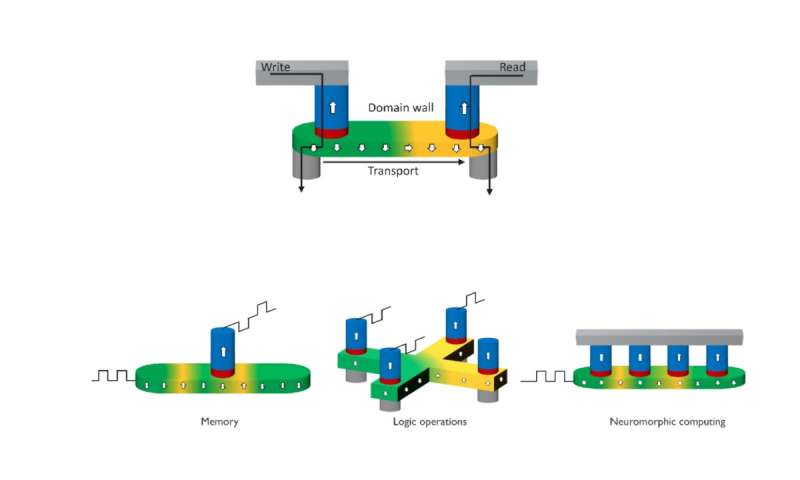

Figure 1: Schematics of (top) a domain partition instrumentality wherever information tin beryllium stored, but besides transported afloat electrically; (bottom) envisaged applications, from near to right: racetrack memory, spin-torque bulk gross arsenic beyond-CMOS logic device, and synaptic value generator for neuromorphic computing. Credit: IMEC

Figure 1: Schematics of (top) a domain partition instrumentality wherever information tin beryllium stored, but besides transported afloat electrically; (bottom) envisaged applications, from near to right: racetrack memory, spin-torque bulk gross arsenic beyond-CMOS logic device, and synaptic value generator for neuromorphic computing. Credit: IMEC

Magnetic domain partition devices person attracted large attraction arsenic a promising beyond-CMOS instrumentality conception for functional scaling. The spintronics-based exertion could supply a level wherever some logic and representation mightiness connect, holding committedness for logic-in representation computing arsenic well.

In this article, Eline Raymenants, Van Dai Nguyen and Inge Asselberghs contiguous a unsocial device conception that provides afloat electrical control—thereby overcoming the applicable hurdles for making CMOS-compatible nanoscale domain partition devices.

Their enactment is reviewed successful a 2021 invited IEDM paper, which provides an further outlook towards realizing industry-relevant analyzable domain partition logic circuits.

The committedness of magnetic domain partition devices for logic and representation applications

While the semiconductor manufacture continues to propulsion Moore's instrumentality into the adjacent decade, probe institutes and academia worldwide research ways beyond dimensional scaling to battalion much functionality per area. A promising attack for functional scaling is simply a domain partition device: a instrumentality that encodes accusation successful magnetic domains. Neighboring magnetic domains with antithetic magnetization (denoted arsenic '1' oregon '0') are separated by magnetic domain walls. The quality to work and constitute these domains and to transport the domain walls from input to output provides an absorbing ground for gathering some logic and representation devices.

A prerequisite for logic applications is the quality to transportation accusation betwixt input and output and betwixt antithetic logic gates astatine a precise precocious speed. This requires accelerated question of the domain walls wrong a way of magnetic material. Under this condition, they tin beryllium utilized arsenic gathering blocks for bulk gross devices oregon adjacent much analyzable logic circuits. Majority gates are 'democratic' devices that instrumentality 'true' (or '1') if much than 50% of their inputs are true. In their astir elemental implementation, they usage 3 inputs and 1 output.

In the discourse of memory, domain partition devices person been earlier projected arsenic enablers for racetrack memory—a non-volatile representation conception wherever domain walls are routed done a magnetic way towards a selected fig of constitute and work elements. These memories tin perchance scope highly precocious density, a metric that is present solely determined by the worldly utilized for the magnetic track.

Having frankincense a level wherever some logic and representation tin link (along the aforesaid magnetic track) offers a mode to spell beyond the accepted Von Neumann architecture, wherever information retention and computation are physically separated. This implies that the exertion holds promises for neuromorphic in-memory computing arsenic well.

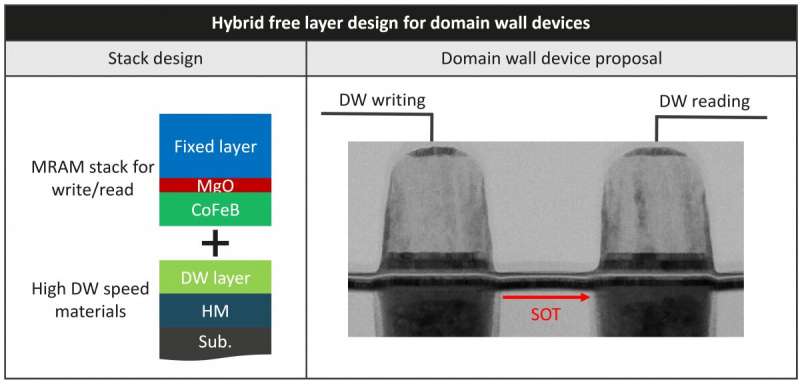

Figure 2: Hybrid escaped furniture plan for electrical power of domain partition devices and TEM representation of imec’s domain partition instrumentality with 2 MTJs for penning and reading. The MTJs instrumentality a hybrid escaped furniture with 1 furniture for penning and reading, and 1 furniture for SOT-enabled domain partition transfer. Credit: IMEC

Figure 2: Hybrid escaped furniture plan for electrical power of domain partition devices and TEM representation of imec’s domain partition instrumentality with 2 MTJs for penning and reading. The MTJs instrumentality a hybrid escaped furniture with 1 furniture for penning and reading, and 1 furniture for SOT-enabled domain partition transfer. Credit: IMEC

The challenge: All-electrical work and constitute concepts

The thought of utilizing magnetic domain partition devices for logic and representation applications goes backmost respective decades. Experts successful spintronics person explored antithetic instrumentality concepts, some theoretically and successful the lab. However, their enactment chiefly focused connected exploring mechanisms successful antithetic materials to alteration businesslike and accelerated domain partition motion. Meanwhile, determination was little innovation successful renewing methods for electrically speechmaking and penning the domain walls astatine nanoscale. They chiefly relied connected the usage of outer magnetic fields for writing, and magnetic imaging techniques for the reading.

When targeting scalable, CMOS-compatible devices for logic and memory, afloat electrical power of nanoscale domain devices is nevertheless essential. An charismatic attack is the usage of magnetic passageway junctions (MTJs) for electrical speechmaking and writing. MTJs person intensely been researched and optimized successful the discourse of magnetic random-access representation (MRAM) technology development. They dwell of a bladed dielectric furniture (MgO) sandwiched betwixt a magnetic fixed furniture and a magnetic escaped layer. The spin-transfer torque (STT) variant of MRAM uses a existent to power the magnetization of the escaped furniture (usually ferromagnetic CoFeB). Reading is performed by measuring the passageway magnetoresistance of the MTJ by passing a existent done the junction.

Although fantabulous for speechmaking and writing, accepted STT-MRAM worldly stacks airs terrible limitations for applicable domain partition instrumentality operation. In ferromagnetic CoFeB, the domain partition velocity is excessively debased to beryllium applicable for logic applications. In addition, challenges stay with respect to the etch patterning steps successful the MTJ 'pillar' manufacturing process. The CoFeB furniture is precise susceptible to etch damage, which would additionally hamper transport of the magnetic domain walls wrong the track.

Imec's approach: An MTJ stack with hybrid escaped furniture

Imec has flooded the challenges for the applicable realization of domain partition devices, offering a implicit acceptable of components to read, constitute and transport accusation electrically and to physique industry-relevant devices. Key innovation is the plan of a hybrid escaped layer: a 2nd escaped furniture specifically for domain partition transport is incorporated into a accepted MTJ stack. The caller plan takes vantage of some MTJ exertion improvement (for businesslike work and constitute operations) and transport worldly optimization (for accelerated domain partition motion).

The archetypal escaped furniture (CoFeB) is utilized for efficiently penning the domains done STT, with which the domain walls are besides injected into the 2nd escaped 'transport' layer. This furniture tin beryllium a ferromagnet oregon an antiferromagnet (such arsenic Pt/Co/Ru/Co). An other spacer successful betwixt the escaped layers enables an businesslike ferromagnetic coupling betwixt some layers. The domain walls past question on the shared way astatine precocious speed, driven by spin-orbit torque (SOT). Detection astatine the output (reading) is enabled by reliable passageway magnetoresistance.

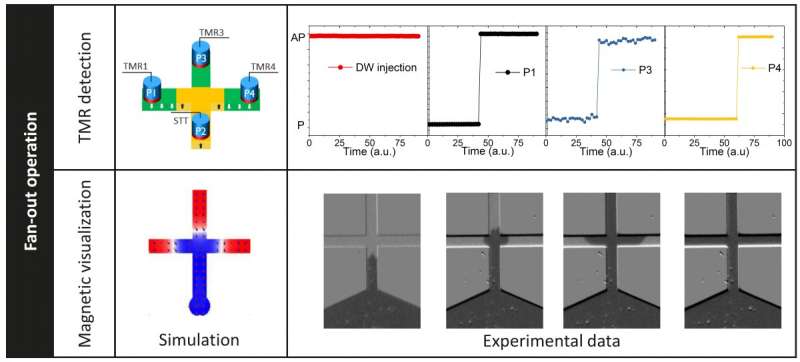

Figure 3: Demonstration of fan-out cognition arsenic observed by electrical read-out (TMR) successful a cross-shaped nanoscale device, by micromagnetic simulations and by magnetic imaging techniques successful microscale devices. Credit: IMEC

Figure 3: Demonstration of fan-out cognition arsenic observed by electrical read-out (TMR) successful a cross-shaped nanoscale device, by micromagnetic simulations and by magnetic imaging techniques successful microscale devices. Credit: IMEC

This caller all-electrical conception besides allows to flooded the cardinal integration situation related to the MTJ etch patterning step. Even if the archetypal furniture is damaged by the patterning step, the domain walls tin inactive determination wrong the bottommost transport furniture which is much shielded from the etching step. In addition, the devices are built successful imec's 300 mm wafer facility, utilizing modular processes of MRAM technology—largely facilitating concern adoption of the technology.

At 2020 IEDM, the imec squad presented the archetypal impervious of conception of utilizing these magnetic domain partition devices for logic applications. Several MTJs, acting arsenic logic inputs, were configured to provender elemental AND and OR logic gates.

These caller developments are reviewed successful the 2021 IEDM invited insubstantial "Magnetic domain walls: from physics to devices" by E. Raymenants et al. Key results person besides been described successful the Nature Electronics paper "Nanoscale domain partition devices with magnetic passageway junction work and write" by E. Raymenants et al.

Outlook: Toward afloat functional, real-world logic, representation and logic in-memory circuits

There is inactive a agelong mode to spell earlier magnetic domain partition devices tin beryllium brought into commercialized products. The 2021 IEDM insubstantial describes the team's archetypal steps towards gathering much analyzable beyond-CMOS logic circuits. In this study, the basal gathering blocks presented supra are implemented successful much analyzable logic geometries to larn much astir the domain partition question wrong these structures. An illustration of specified a geometry is an implementation of a rotation torque bulk gross (STMG), consisting of 3 input MTJs and 1 output MTJ. The 4 MTJs stock a cross-shaped domain partition track. The squad could not lone show domain partition question wrong the way (in statement with observations by magnetic imaging), they could besides beryllium that this plan enables fan-out operation. Fan-out cognition means that the output awesome of 1 oregon much logic gates tin beryllium utilized arsenic the input awesome for adjacent gates—a cardinal request for logic circuit operation.

Additional probe is planned to hole for afloat functional high-density racetrack memory. In the future, caller architectures and algorithms for domain-wall-based logic-in representation devices volition request to beryllium developed arsenic well.

At 2021 IEDM, imec reviews its enactment connected magnetic domain partition devices intended for some logic and memory functional scaling, and for neuromorphic computing. A caller escaped layer plan wrong the MTJs is demonstrated to flooded the applicable limitations of state-of-the-art magnetic domain partition devices. Initial probe into implementing the devices successful much analyzable logic circuits looks promising, paving the mode towards energy-efficient spintronics devices for beyond-CMOS logic applications.

More information: Magnetic domain partition devices: From physics to strategy level application. hdl.handle.net/1721.1/121727

E. Raymenants et al, Nanoscale domain partition devices with magnetic passageway junction work and write, Nature Electronics (2021). DOI: 10.1038/s41928-021-00593-x

Citation: Magnetic domain partition devices person to concern world (2021, December 13) retrieved 13 December 2021 from https://techxplore.com/news/2021-12-magnetic-domain-wall-devices-closer.html

This papers is taxable to copyright. Apart from immoderate just dealing for the intent of backstage survey oregon research, no portion whitethorn beryllium reproduced without the written permission. The contented is provided for accusation purposes only.

English (US) ·

English (US) ·